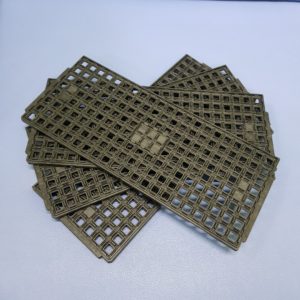

JEDEC IC tray is designed and made for the safe handling , transport and storage of Integrated Circuits (ICs), modules and other components. JEDEC is a list of specifications for matrix trays which are constructed from molding compounds, though other materials such as aluminum are permissible. JEDEC IC trays are strong, with minimum twist, to hold and protect its contents.

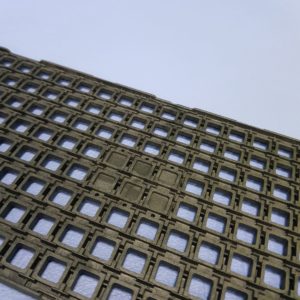

The outline dimensions of of all JEDEC matrix trays are 322.6 x 136mm. Low profile trays are with thickness of 6.35mm accommodate 90% of all standard components, such as BGA, CSP, QFP, TQFP, QFN, TSOP and SOIC. A high profile 10.16mm version is designed to hold thick (high) components such as PLCC, QUAD, PGA, modules and assemblies.

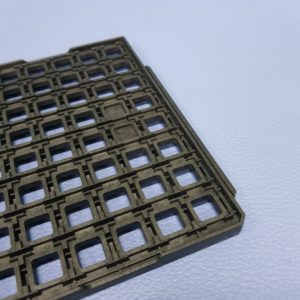

Standard design features:

- Flat cells in the center area to allow automated handling by vacuum pick up tools

- Scalloped feature at one side of the tray to allow the use of a pin to mechanically fix correct orientation during use

- 45-degree chamfer in one corner to provides visual indicator of Pin 1 orientation of the IC

- Stackable within the same device family and maker’s model to 5-7 tray

- In Multiple colors to allow easy identification of lots and classification.

Typical temperature ratings for bakeable JEDEC trays are: 140°C, 150°C and 180°C. Higher temperature trays cost more. Normally baking is done at 125°C. Typically, 140°C trays are sufficient to maintain dimensional stability during baking. Non-bakeable trays rated at 50~75°C are also available.

www.Skymart-Technologies.com